Design of an FPGA to realize the function of watchdog circuit

1 Introduction

In communication and digital systems, if there are design defects or accidental interference in the circuit such as single-chip microcomputer and DSP, the system will not operate normally, and the crash will occur, which will cause greater harm to the whole circuit. It is necessary to reset the system in time. This paper applies FPGA design to realize a fast response watchdog circuit, which can provide fast response monitoring for circuits such as single chip microcomputer, DSP and microprocessor. In this circuit, the overall design uses FPGA devices, which greatly improves the overall performance and speed of the circuit.

2, fast response watchdog circuit structure

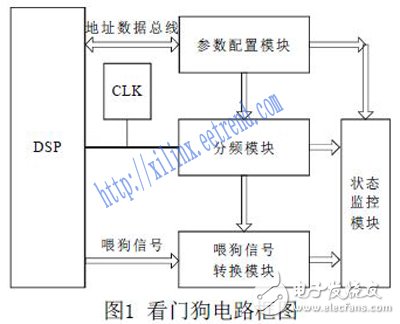

Figure 1 is a block diagram of the designed watchdog circuit. The frequency dividing module is a clock generating module of the watchdog circuit; the parameter configuration module receives the parameter configuration information sent by the external data address bus, extracts the information, and transmits the information to the clock frequency dividing module and the state monitoring module; the feeding dog signal conversion module is based on The dog feeding method of the monitored object converts the different types of feeding dog signals into standard unified pulse signals. For the way of feeding the dog, the single I/O port can be alternately written with '0' and '1', or The address data bus is used to write the pre-agreed data command; the status monitoring module monitors the input standard unified dog signal.

3, simulation verification

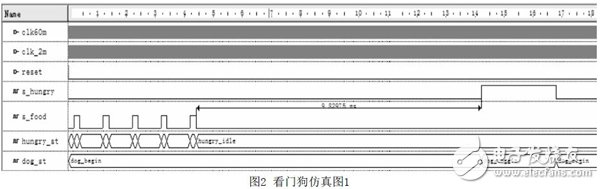

This design is implemented by the Xilinx Spartan series of FPGAs. The simulation results are shown in Figure 2. As shown in the figure, clk60m and clk_2m signals are clock input signals, clk60m is from the working clock of the external DSP, clk_2m is the operating clock of the watchdog; reset is the circuit power-on reset signal; s_food is fed the dog signal through the feed dog signal conversion module The output dog signal; hungry_st and dog_st are state machine signals of the status monitoring module; s_hungry is the monitoring alarm signal output by the status monitoring module. It can be seen from the figure that when the feeding dog signal pulse disappears for about 10 ms, the s_hungry monitoring signal is generated, and the response speed of the monitoring signal can be freely adjusted according to the actual use requirement. Compared to the traditional reset response speed of the watchdog circuit in seconds [2], the response speed of the circuit is increased to the order of milliseconds.

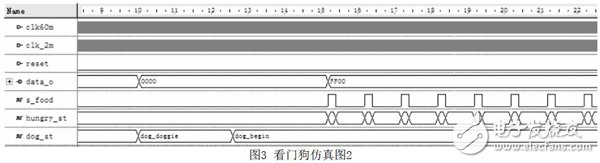

As can be seen from Fig. 3, the original signal of the feeding dog is data_o, which is converted into a standard pulse feeding dog signal s_food by the feeding dog signal conversion module, and the standard s_food output state monitoring module performs state monitoring.

4, the conclusion

This paper adopts FPGA design to realize a simple and feasible watchdog circuit, which can quickly monitor and monitor the real-time processing digital system. This circuit makes up for the lack of traditional watchdog circuit, and has good versatility, scalability and flexible configuration. Features such as digital systems for a variety of real-time processing.

references

[1] Li Yajie. A design method for reset signal of FPGA+multi-DSP system. Microcomputer information. Embedded and SOC.2010, 05.

[2] Li Bingyu, Wang Xiaodong. A method for implementing the function of watchdog circuit in FPGA. Technical application.

[3] Wang Yehui, Lin Yuxia, Yan Wei. CPLD implementation of monitoring and tracking timer circuit. Electronic Engineer. Measurement and Control Technology and Equipment, 2003, 29 (12).

Moen Garbage Disposal,Cleaning Garbage Disposal,Kitchenaid Garbage Disposal,Removing Garbage Disposal

Xinhe Stainless Steel Products Co., Ltd. Of Pengjiang District Jiangmen City , https://www.sinkhall.com